Frequenzteiler

Wir erweitern unsere Taktgeber-Schaltung nun um zwei Frequenzteiler-Stufen. Das lässt sich mit D-Flipflops oder JK-Flipflops erreichen.

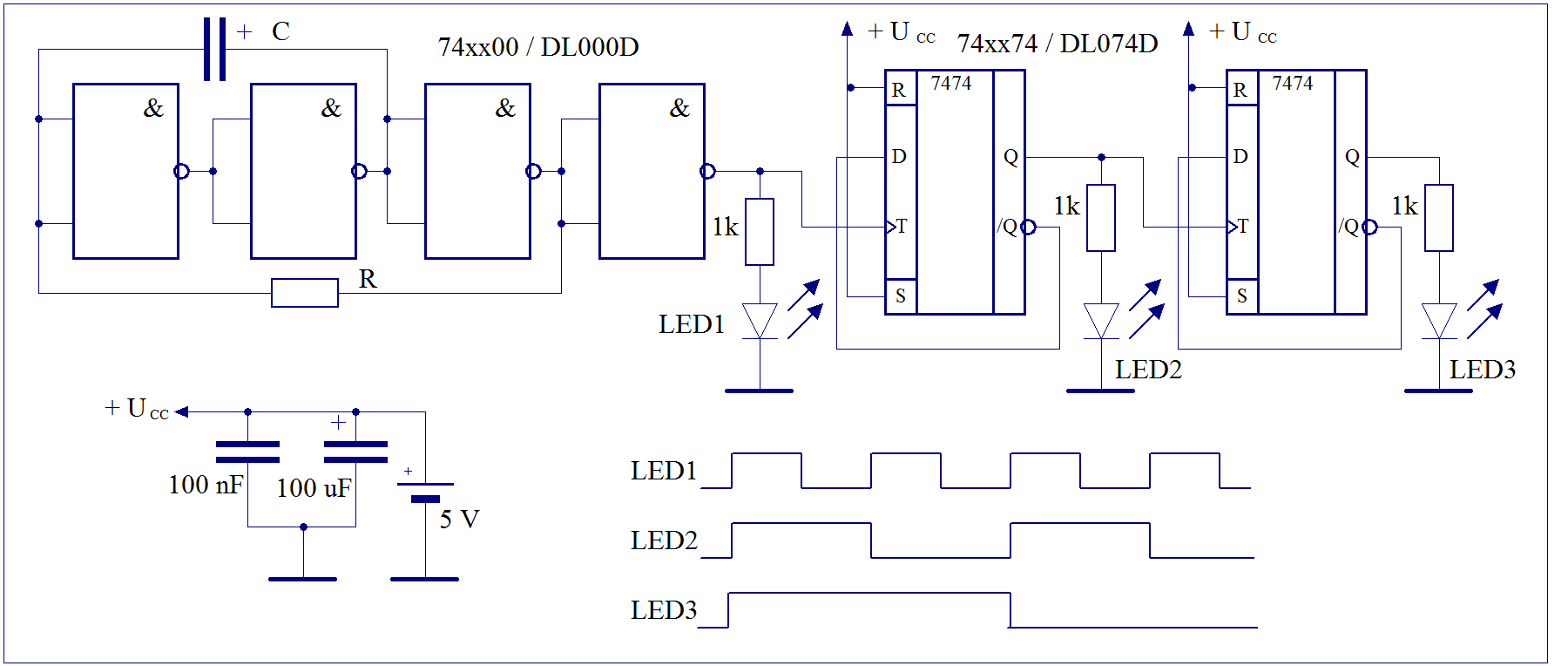

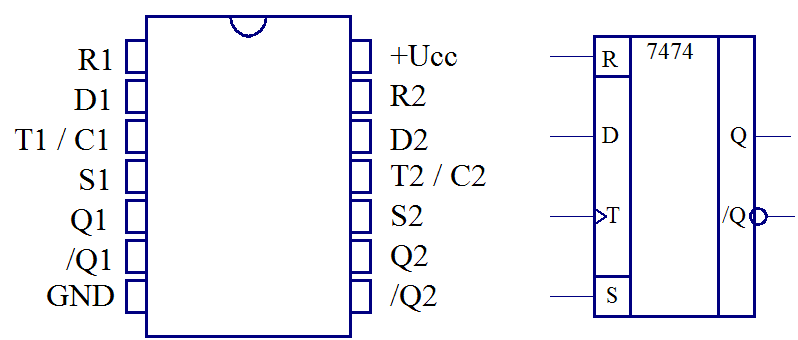

Frequenzteiler mit DL074D / 7474 / 74LS74 (TTL/LS-TTL-Gatter)

-> enthält 2 taktflankengesteuertes D-Flipflop

Die Rückführung von /Q auf D macht aus dem D-Flipflop ein T-Flipflop!

In dieser Beschaltung des 74xx74 wird aus dem D-Flipflop ein T-Flipflop, das bei jeder L-H-Taktflanke den Ausgang Q bzw /Q "hin- und her schaltet". Dadurch wird der Eingangstakt (also die Frequenz des Taktes) halbiert.

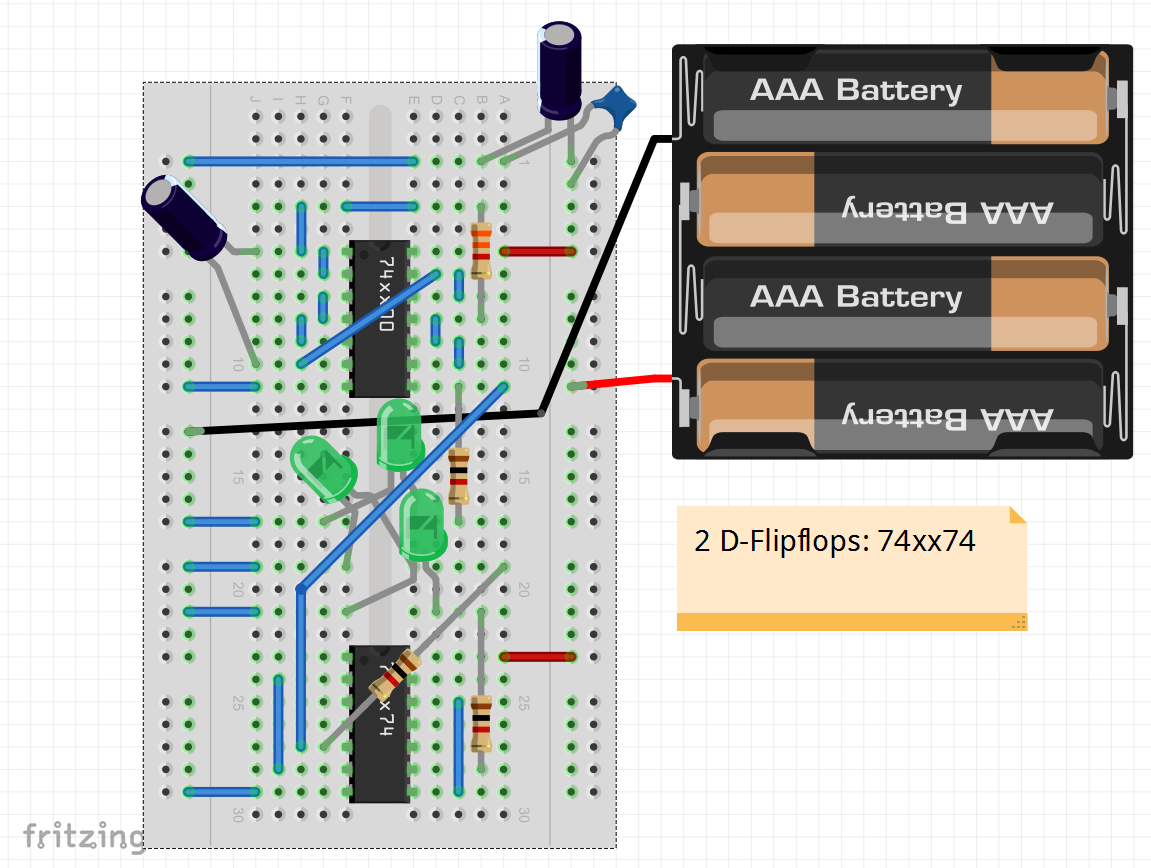

Aufbauvorschlag Steckbrett

ACHTUNG: Eigentlich müssten die R-undS-Eingänge an HIGH (5 Volt) gelegt werden. Bei TTL-Gattern haben aber unbeschaltete Eingänge automatisch HIGH, so dass ich darauf verzichtet habe.

Bei CMOS-Gattern würden unbeschaltete Eingänge meist zu chaotischem Verhalten führen, da diese Eingänge sehr hochohmig sind und auf alle möglichen Störungen (Netzbrummen, Gewitter, Handkapazitäten usw.) reagieren.

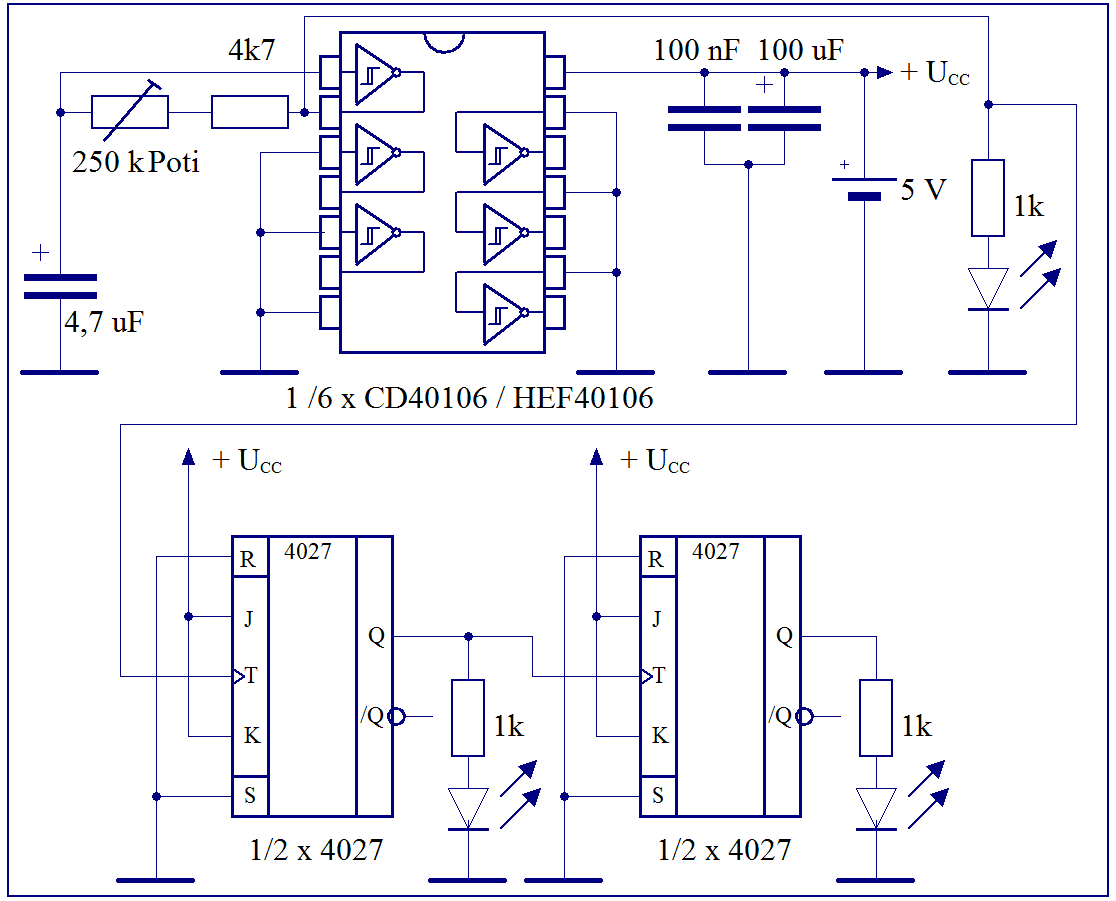

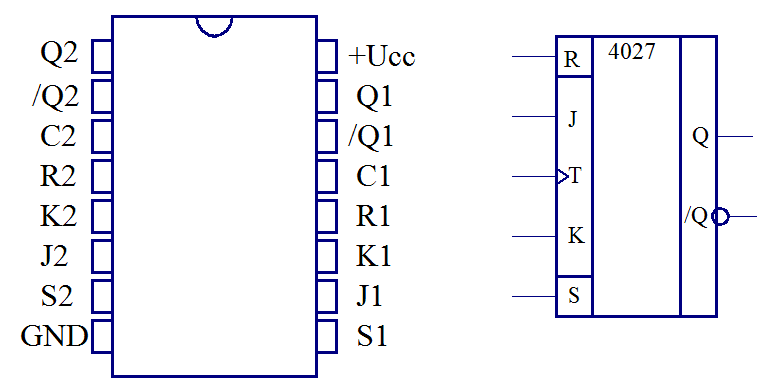

Frequenzteiler mit 4027 (2 Stück CMOS-J-K-Flipflops)

Als Taktgeber dient ein 1/4 CMOS-Schmitt-Trigger 40106. Die Betriebsspannung könnte bei kompletter CMOS-Bestückung auch höher als 5 Volt sein. Zugelassen sind 3 bis 15 Volt für Ucc.

Das Verhalten dieser Frequenzteiler-Schaltung entspricht komplett der oben gezeigten mit TTL-Gattern. Auchn hier sind die Flipflops als T-Flipflop (Toggle-Flipflop) geschaltet:

Siehe auch hier:

![]() "Digitalelektronik Polytechnische Schule" von Josef Stiegler

"Digitalelektronik Polytechnische Schule" von Josef Stiegler

![]() "Schaltwerke und Flipflops" von Prof. Plathe

"Schaltwerke und Flipflops" von Prof. Plathe

.